芯粒集成工艺技术发展与挑战

陈浪1,杜建宇1,汪琪1,张盼1,2,张驰1,2,王玮1,2 (1.北京大学集成电路学院;2.北京大学微米纳米加工技术全国重点实验室)

摘要:万物感知、万物互连和万物智能推动集成电路进入新一轮的高速发展期并促进对高性能芯片需求的指数级增长。后摩尔时代,芯片性能的进一步提升面临大面积芯片良率降低、功耗控制难、片内互连密度大以及制造成本高等难题。因此业界开始将原来多功能、高集成度的复杂SoC 芯片分割做成单独的芯粒(Chiplet),再通过先进封装工艺集成为集成芯片或微系统产品。对芯粒集成技术特征及模式、发展历史、优缺点进行了梳理与阐述,同时归纳总结了芯粒集成的关键技术挑战,并对未来发展进行了展望。

关键词:芯粒集成;互连密度;热管理;微系统

目录介绍

0 引言

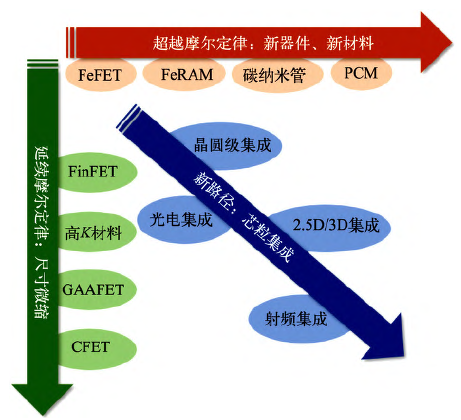

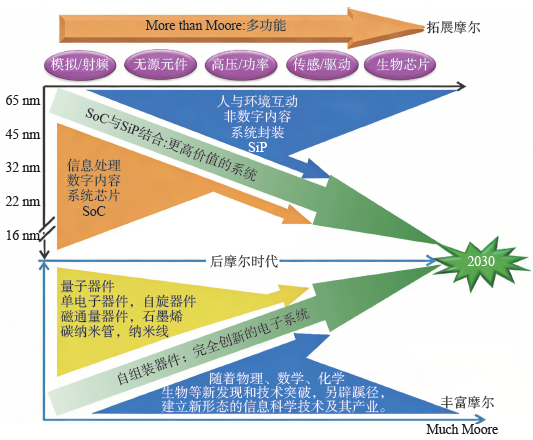

1 芯片性能提升路径

2 芯粒集成核心结构及关键工艺

2.1 层内互连

2.2 层间互连

2.3 跨层互连

3 芯粒集成模式

3.1 CoWoS技术

3.2 EMIB技术

3.3 InFO技术

3.4 eSiFO技术

3.5 SoIC技术

3.6 典型封装技术对比

4 芯粒集成技术挑战及展望

1)芯粒间的高密度互连工艺设计

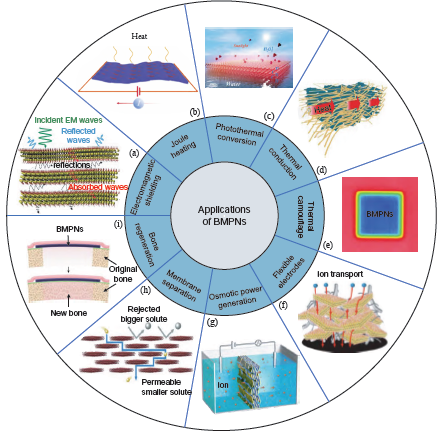

2)材料-结构-工艺协同设计

3)封装结构的热-力可靠性

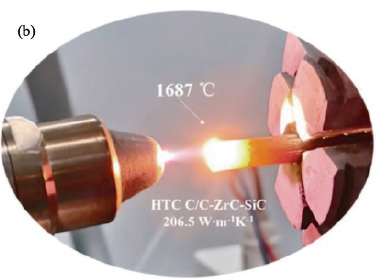

4)先进热管理技术开发

5)多频域、多模态的芯粒集成微系统设计

5 结束语

©软件著作权归作者所有。本站所有文件均来源于网络,仅供学习使用,请支持正版!

转载请注明出处!

发表评论 取消回复