CVD多晶金刚石膜的生长技术与热导率优化研究进展

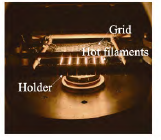

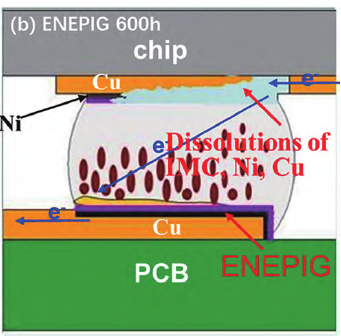

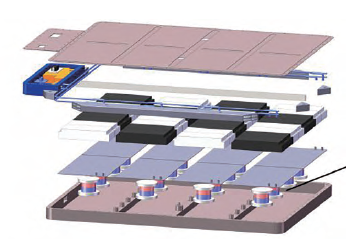

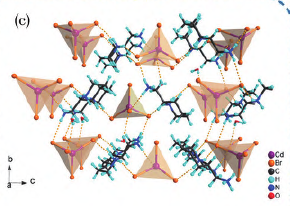

摘要:系统综述了化学气相沉积(CVD)技术在多晶金刚石膜生长与热导率优化领域的研究进展,聚焦大尺寸制备技术突破及热性能调控机制。通过对比热丝化学气相沉积(HFCVD)、微波等离子体化学气相沉积(MPCVD)、直流热阴极化学气相沉积(DC-HC CVD)及直流电弧等离子体喷射化学气相沉积(DC arc jet CVD)等主流方法的工艺特点,揭示了各类技术在大尺寸金刚石膜制备中的优势与局限性。研究指出,大尺寸金刚石膜的制备需结合反应器设计创新、等离子体激发模式优化及多参数协同调控,以实现高效、均匀的规模化生产。在热导率优化方面,研究系统分析了晶粒尺寸、膜厚、晶面取向及残余应力等多因素的协同作用。通过优化晶粒尺寸与膜厚的匹配关系,显著降低了晶界密度对声子传输的散射效应,从而提升整体热输运效率。工艺参数中,碳源浓度、温度与功率的精准调控对晶粒形貌与结晶质量具有决定性影响,晶面取向的择优生长可进一步强化热导率优势。动态磁场辅助、基团比例调控等创新方法为晶面定向生长提供了新路径。残余应力问题则需通过衬底选择、界面预处理及结构设计等策略综合缓解,以降低晶格畸变对热性能的负面影响。为高性能金刚石热管理材料的开发及高功率电子器件的散热应用提供了理论框架与技术参考。